## Low Power Design

Hussam Amrouch, Volker Wenzel on behalf of Prof. Dr. Jörg Henkel Summer Term 2016

CES – Chair for Embedded Systems

Volker Wenzel

## **Overview Low Power Design Lecture**

- Introduction and Energy/Power Sources (1)

- Energy/Power Sources(2): Solar Energy Harvesting

- Battery Modeling Part 1

- Battery Modeling Part 2

- Hardware power optimization and estimation Part 1

- Hardware power optimization and estimation Part 2

- Hardware power optimization and estimation Part 3

- Low Power Software and Compiler

- Thermal Management Part 1

- Thermal Management Part 2

- Aging Mechanisms in integrated circuits

- Lab Meeting

- Introduction of Theoretical Background (Volker)

- Lab Demo (Hussam)

- Thermal Simulation

- estimate thermal profile from power trace in different of blocks (e.g. using HotSpot)

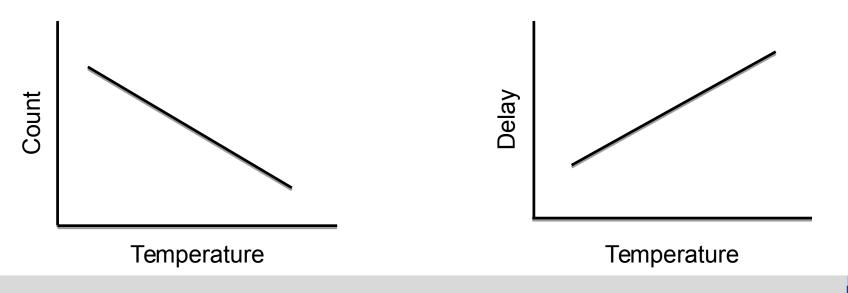

- Thermal Sensor

- hard sensor (e.g. thermal diode)

- soft sensor (e.g. ring oscillator)

- Thermal Camera

- very accurate reading

- Thermal image shows actual temperature distibution across chip

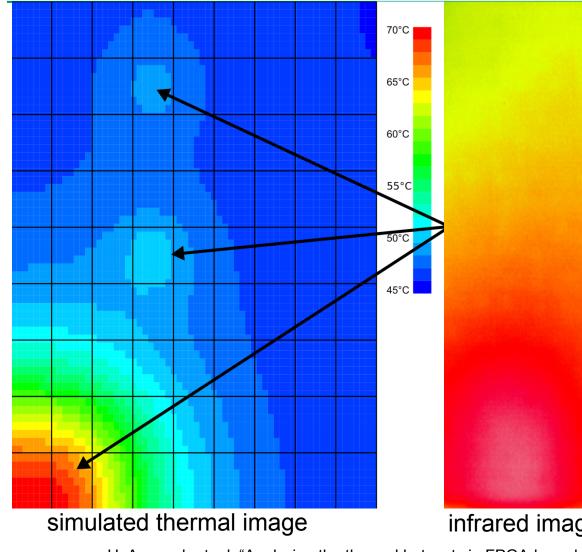

- comparison of HotSpot and measurement w/ thermal camera (next slide)

- issues w/ on-chip sensors

- calibration

- chip area

- gradients, inhomogeneous heat distribution; thermal diode might measure the wrong spot of the chip

- thermal camera superior way of measuring temperature

## HotSpot Simulation of FPGAs

src: H. Amrouch et. al, "Analyzing the thermal hotspots in FPGA-based embedded systems," FPL, 2013.

More than 10°C difference between the reading of sensor and the real peak temperature.

The potential hotspot

reaches 94°C and is

located at the corner of

93.9 °C Temp max: 93.9 °C Temp min: 70.9 °C Thermal variation: 23°C 91.0 °C 88.5 °C Src: H. Amrouch, J. Henkel 86.0 °C ard sensor 83.5 °C 81.0 °C 78.5 °C 76.0 °C 73.5 °C 71.0 °C Xilinx Virtex-5, 65nm

chip

Soft sensors (e.g. ring oscillator):

- + low power consumption

- + low area overhead

- $\rightarrow$  Many can be placed across the chip

- requires calibration (e.g. central hard sensor)

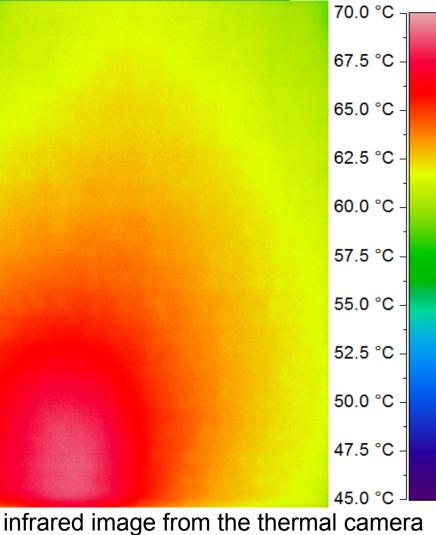

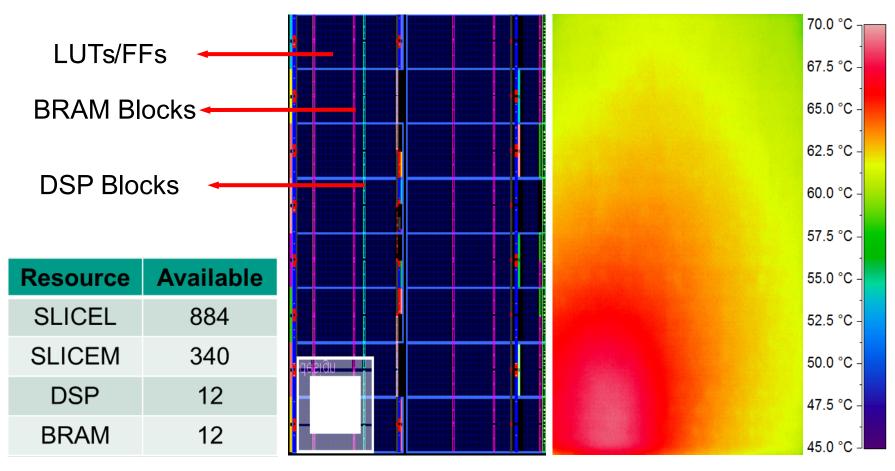

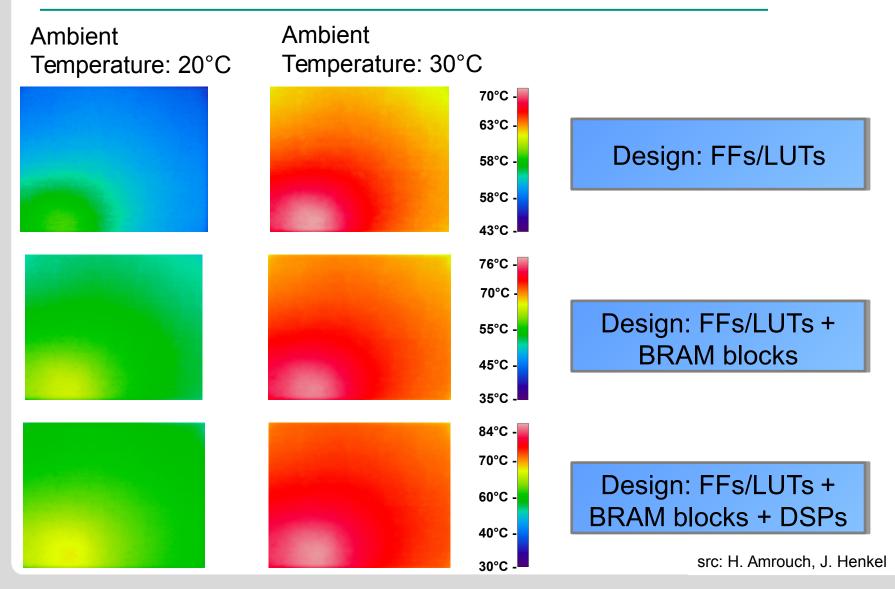

## **Thermal behavior in FPGA**

Tested region properties

FPGA Floorplan (Xilinx Virtex-5) Infrared image obtained from our thermal setup

11

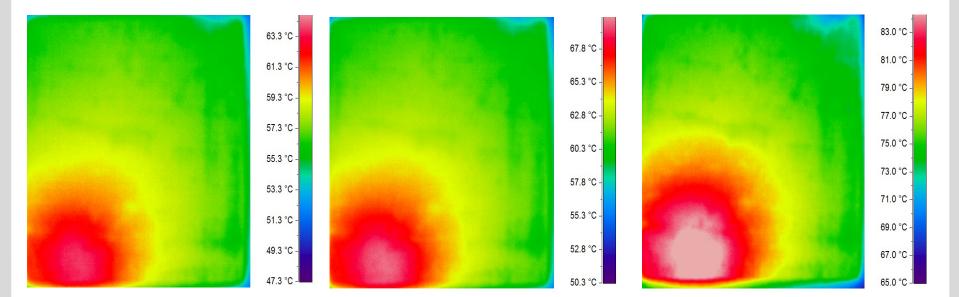

Design: Only-Slices Peak Temp = 64°C Thermal variation = 13°C Design: Slices+BRAMs Peak Temp = 70°C Thermal variation = 15°C Design: Slices+BRAMs+DSPs Peak Temp = 86°C Thermal variation = 19°C

```

Slices = LUTs + FFs, ambient temp = 30°C

```

Src: H. Amrouch, J. Henkel

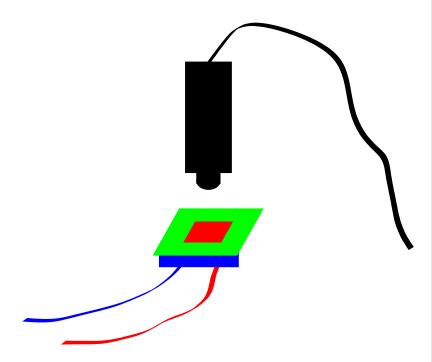

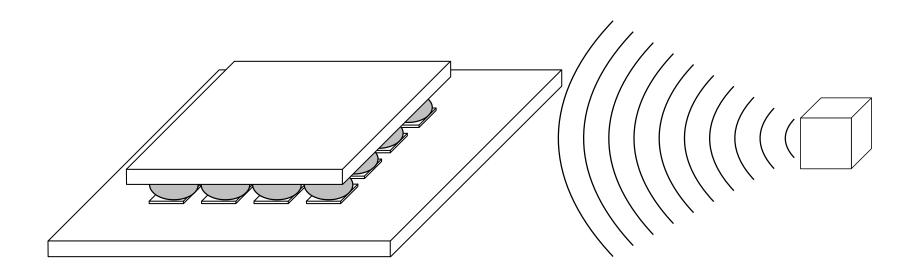

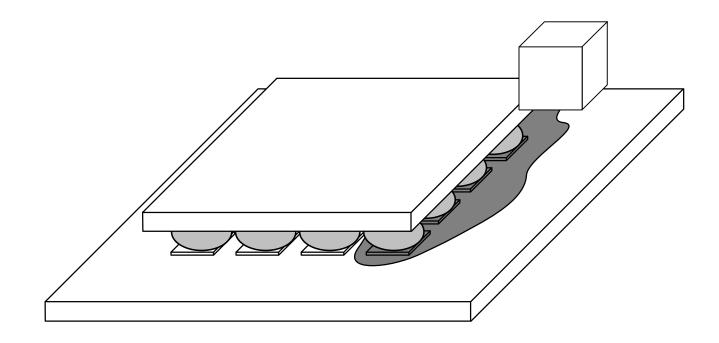

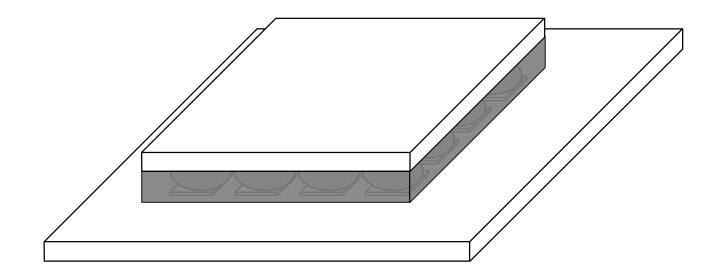

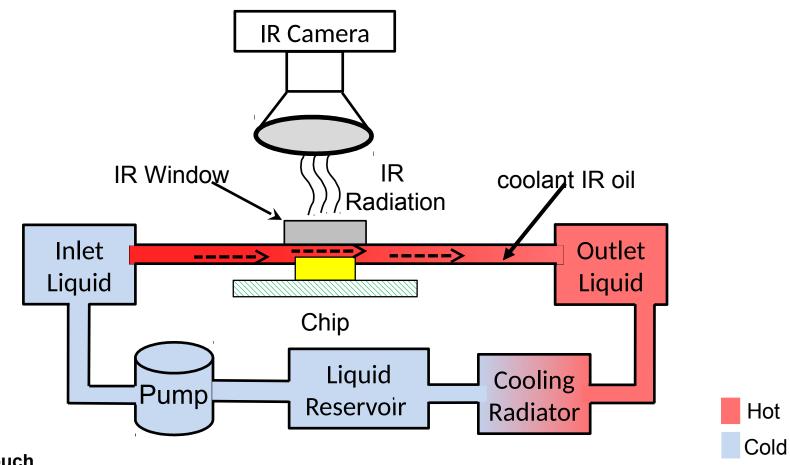

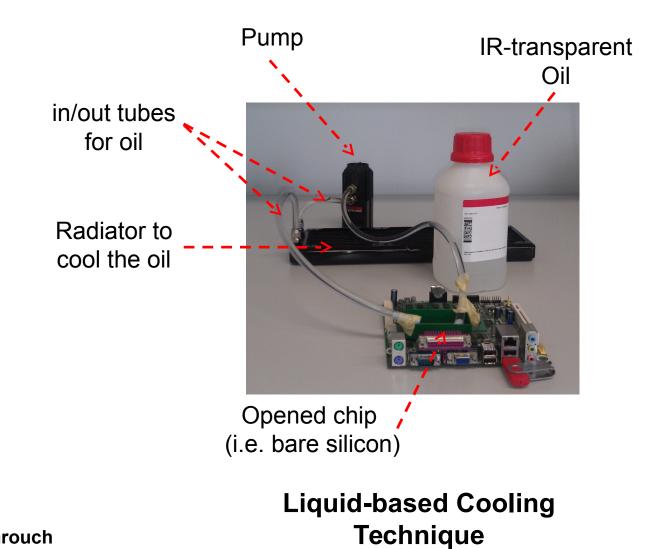

**Thermal Setup**

- need to remove packaging from chip

- alternative approach: IR-oil

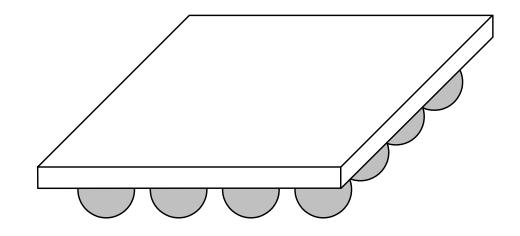

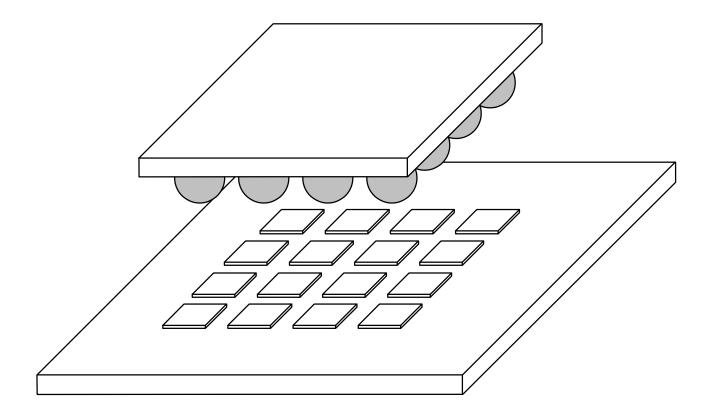

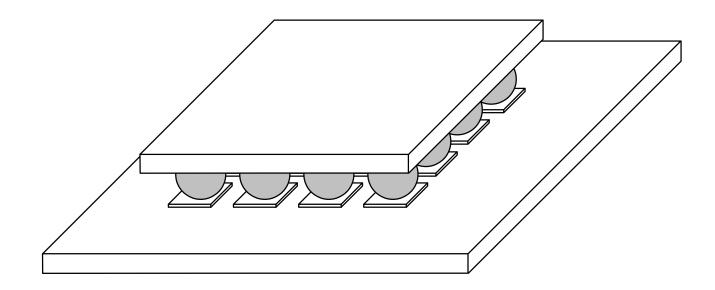

- controlled collapse chip connection (C4) aka Flip Chips

- bare silicon must be visible with packaging removed

#### Integrated circuits are created on the wafer

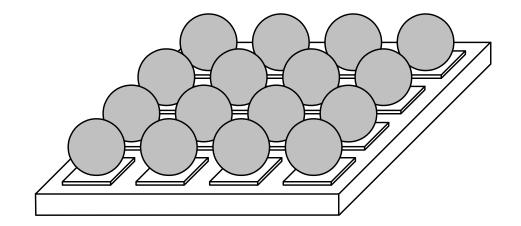

## Fabrication of Flip Chips

## Fabrication of Flip Chips

- infrared camera

- 8µm-14µm

- precise, contact-less temperature measurement

DIAS PyroView 380L compact src: DIAS

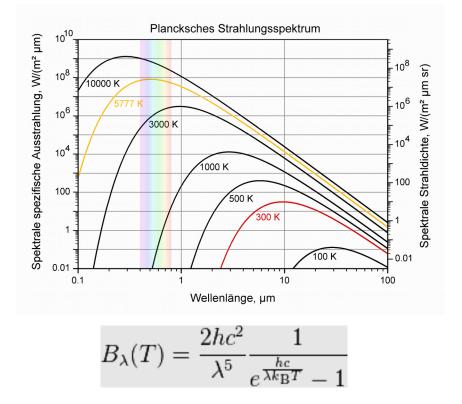

- hot bodies radiate!

- spectrum is characteristic of equilibrium temperature

- infrared for usual temperatures

$$P = \sigma A T^4$$

#### src:en.wikipedia.org

- idealized physical body

- absorbs all incident radiation

- is in thermal equilibrium

- optimal diffuse emitter

- real bodies: emissivity ε

- = energy emitted / energy emitted by black body at the same temperature

- ε between 0 and 1

ces.itec.kit.edu

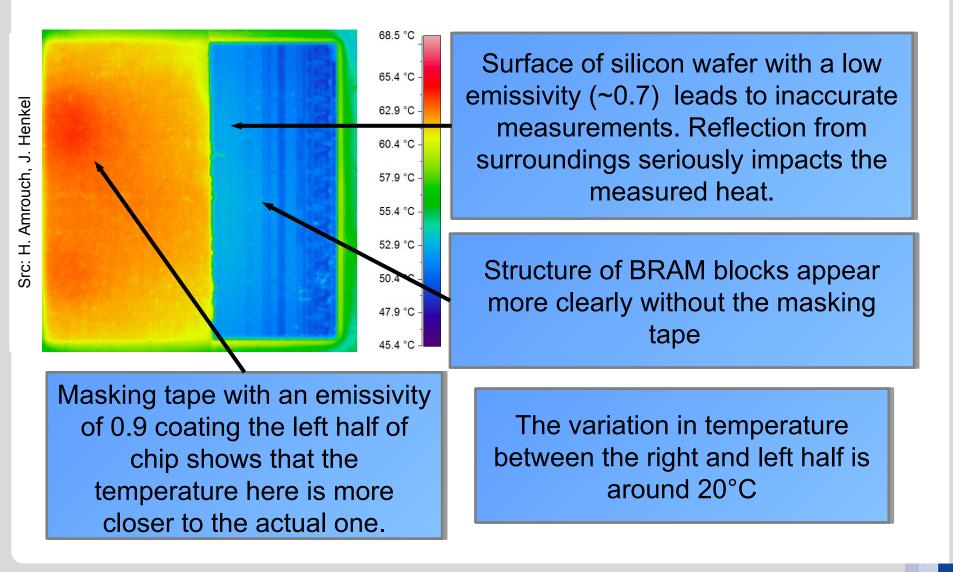

## **Emissivity Problem**

## Impact of ambient temperature

Volker Wenzel

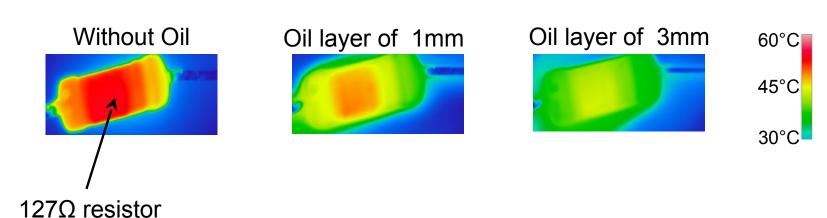

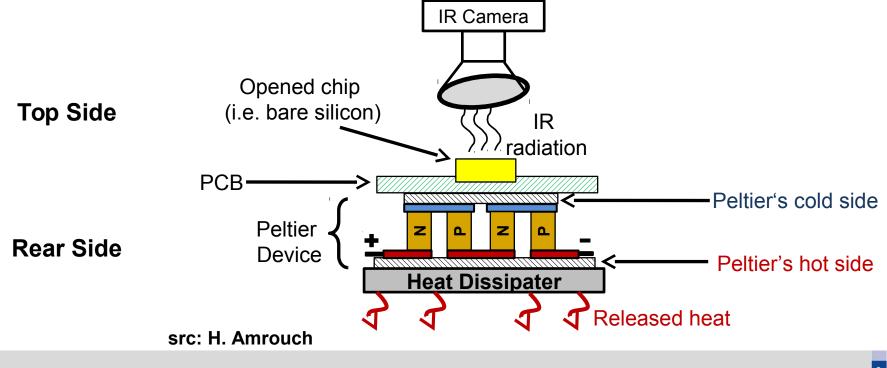

Major Challenge: Constructing IR-transparent cooling that

- allows the IR radiation emitted from the chip to reach the thermal camera.

- prevents the chip from burning up.

Src: H. Amrouch

Volker Wenzel

ces.itec.kit.edu

## **IR Thermography: State-of-the-Art**

Src: H. Amrouch

connected to 4V

# Thermal convection destroys the clarity of the captured IR images

Src: H. Amrouch

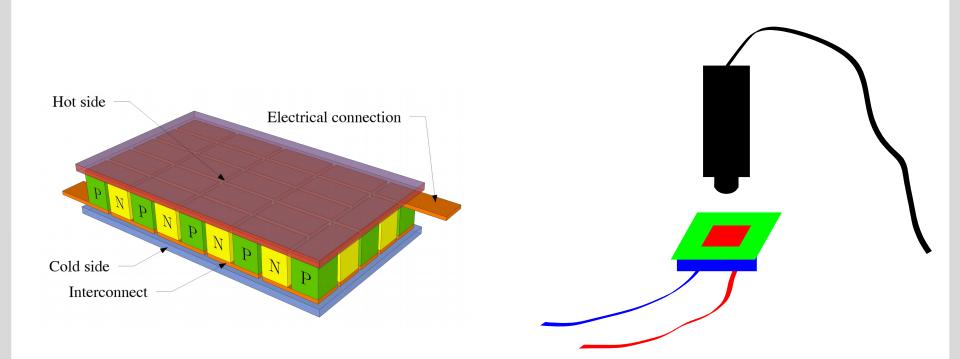

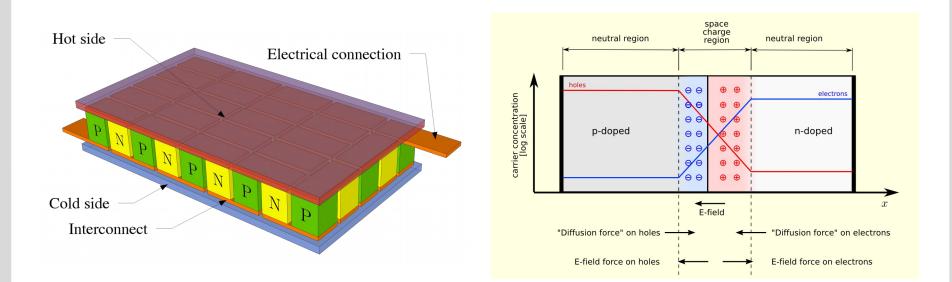

## **Thermoelectric Cooling**

## **Thermoelectric Cooling**

src:enawikipedia.org

## **IR Thermography: Built Thermal Setup**

- It continuously cools the measured chip from its rear side.

- Thermoelectric technology has been employed It provides a stable/controlled source of cooling (Peltier).

ces.itec.kit.edu/69.php